Краткое описание архитектуры микроконтроллера atmega16

Лабораторная работа №4

Изучение основ программирования RISC — микроконтроллеров Гарвардской архитектуры на примере микроконтроллера ATmega16(32) компании Atmel

Краткое описание архитектуры микроконтроллера ATmega16

§ Высокопроизводительный, потребляющий малую мощность 8 разрядный микроконтроллер [МК] Advanced RISC-архитектуры;

§ 131 машинная инструкция;

§ 32 8-разр. регистров общего назначения + регистры управления встроенной периферией;

§ Производительность до 16 млн. операций в секунду (MIPS)при тактовой частоте 16 МГц;

§ Встроенное умножающее устройство выполняет умножение за 2 машинных цикла;

§ 16KBytes в системе программируемой внутренней Flash памяти программ;

§ 512Bytes внутренней перепрограммируемой памяти данных EEPROM;

§ 1KByte внутренней SRAM;

§ Количество циклов записи в флэш — память: 10,000 Flash/100,000 EEPROM;

§ Хранение данных: 20 лет при 85°C/100 лет при 25°C(1);

§ Внутрисистемное программирование встроенной загрузочной программой;

§ Программируемая защита кода программы;

§ Интерфейс SPI для внутрисистемного программирования;

§ Интерфейс JTAG (совместимость со стандартом IEEE 1149.1);

§ Два 8-разрядных таймера/счетчика с отдельным предделителем и режимом сравнения и захвата;

§ Один 16-разрядный Таймер/счетчик с отдельным предделителем, режимом сравнения и захвата;

§ Счетчик реального времени с отдельным внешним кваррцевым генератором;

§ Четыре канала для формирования ШИМ (широтно – импульсной модуляции);

§ 8-канальный аналоговый мультиплексор и 10 разрядный АЦП;

§ 2 встроенных усилителя аналоговых сигналов с программируемым коэффициентом на 1x, 10x, или 200x;

§ Байт-ориентированный двухпроводной последовательный интерфейс I2C

§ Программируемый последовательный USART (аналог RS232)

§ Программируемый сторожевой таймер с встроенным генератором;

§ Встроенный аналоговый компаратор;

§ Внешние и внутренние источники прерываний;

§ Встроенный RC задающий генератор;

§ Шесть режимов снижения энергопотребления:

• холостой ход (Idle);

• уменьшение шумов АЦП;

• экономичный (Power-save);

• выключение (Power-down);

• дежурный (Standby) ;

• и расширенный дежурный (Extended Standby);

§ Программный выбор тактовой частоты;

§ 32 программируемые линии ввода-вывода;

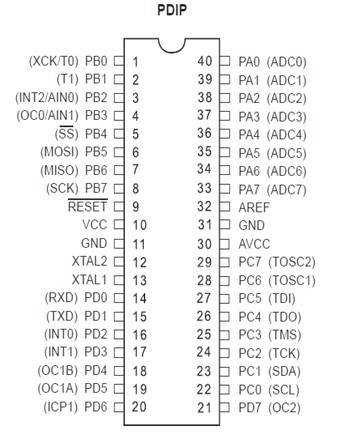

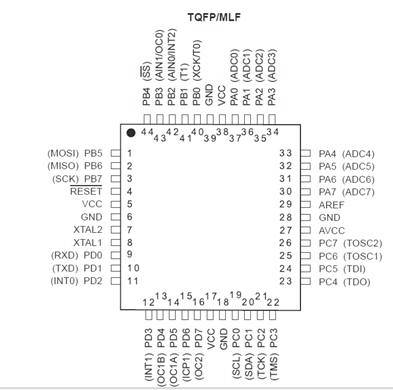

§ Корпус 40-pin PDIP, 44-выводный TQFP;

§ Напряжение питания 2.7 – 5 Вольт;

§ Рабочая частота 0 – 16Мгц;

§ Потребляемый ток

• Active: 0.6 мА

• Режиме ожидания: 0,2 мА

Режим выключения питания:1 мкА

Варианты корпусов:

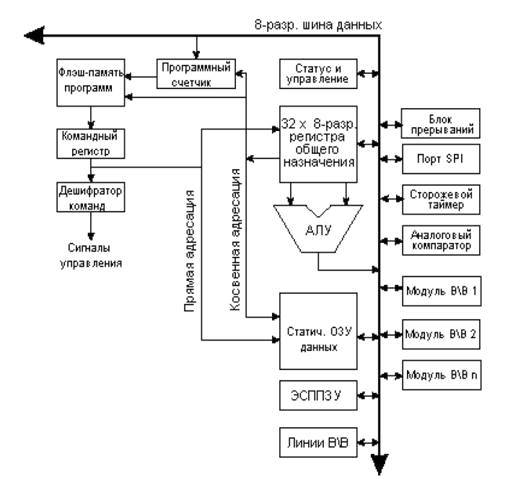

Укрупненная функциональная схема:

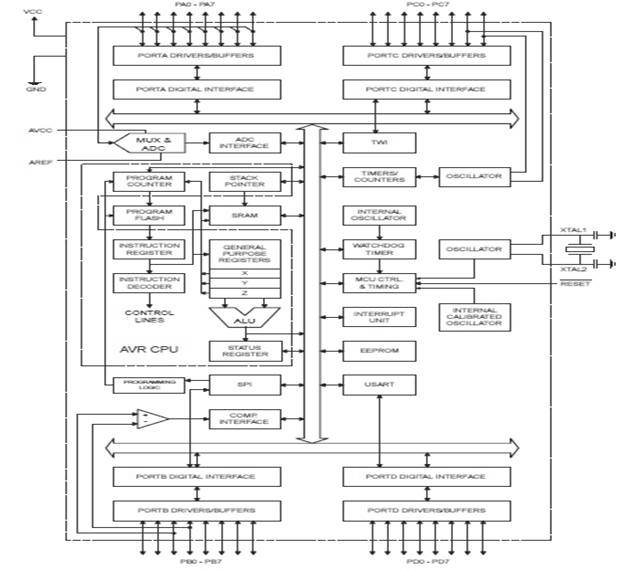

Функциональная схема:

Память программ представляет собой внутрисистемную. программируемую флэш-память в которой хранятся команды управляющие работой МК, а также константы не меняющиеся во время работы.

Для адресации к памяти программ используется счетчик команд.

По адресу $0000 находится вектор сброса. При сбросе МК (вход RESET) выполнение программы начинается с этого адреса.

Память данных состоит из двух независимых не зависимых пространств ( регистровой памяти + SRAM) и EEPROM данных.

Регистровая память состоит из 32 РОН и 4 –х регистров портов ввода –вывода RA, RB, RC, RD.

Порты ввода вывода.

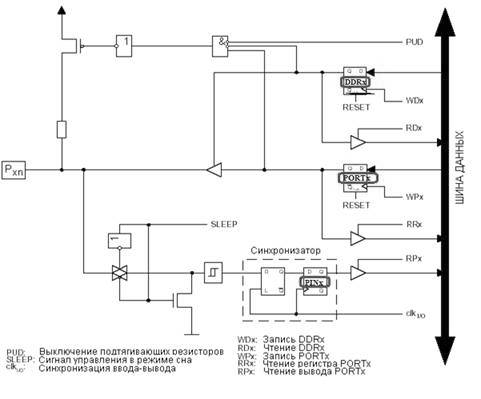

С каждым выводом микроконтроллера связывается бит в трех регистрах регистрах DDRx и PORTx и PINx.

Регистр DDRx задает направление передачи. При DDRx=1 — вывод информации (выход). При этом выводимая информация (0 или 1) записывается в регистр PORTx и после этого появляется на выводе Pxn.

При DDRx=1 вывод настраивается на ввод (вход). При этом вводимая информация появляется в регистре PINx. В том случае если PORTx = 1, то ножка микроконтроллера подключается (подтягивается ) через высокоомный резистор к напряжению питания (+5В). Это режим используется, когда надо подтянуть не используемые выводы к напряжению питания для исключения помех, которые могут на нем появится и нарушить работу МК. Если PORTx = 0, то вход переходит в третье (высокоомное состояние — отключается повисает в воздухе от схемы и не влияет на работу других схем соединенных с этим выводом). Этот режим используется если вывод подключается к общей шине. Таким способом вывод можно отключать и он не будет мешать другим выводам, с ним соединенным.

Настройка нулевого вывода порта С на вывод информации.

DDRC.0=1; PORTC.0 =0; на ножке порта PnC.0 ,появится 0.

DDRC.0=1; PORTC.0 =1; на ножке порта PnC.0 ,появится 1.

Настройка нулевого вывода порта С на ввод информации.

DDRC.0=0; PORTC.1 =0; из бита PINC.0 , можно считать состояние на 0 -ножке порта С. Если к этому порту через кнопку подать 5вольт , то обнаружить факт нажатия на кнопку с учетом задержки на дребезг контактов можно следующим образом

if (PINС.0==1) {for(k=1;k

Если DDRC.0=0; PORTC.1 =1; то будет вход подтянут к напряжению +5В высокоомным резистором.

У каждого вывода порта есть альтернативные функции. Например, вход PD2 может служить просто входом, а может быть настроен на прием сигнала запроса на прерывание INT0.

Включение альтернативных функций происходит в внутренних модулях, поддерживающих альтернативные функции.

Бит PUD = 1 в регистре управления SFIOR отключает все подтягивающие резисторы.

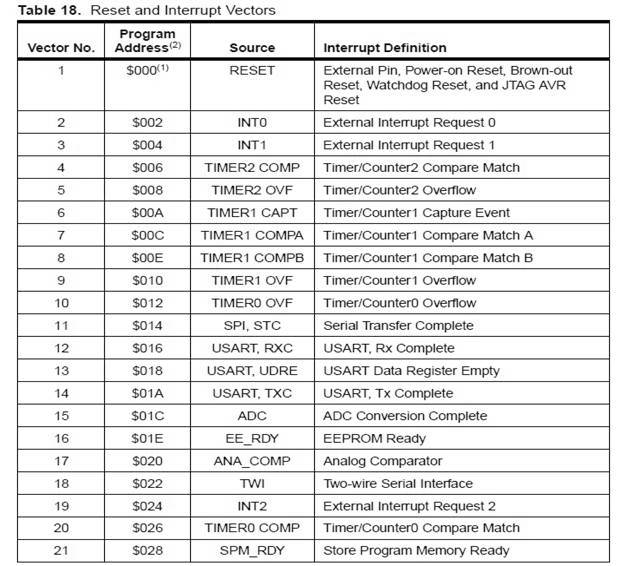

Уровни прерываний, закрепленные за усройствами и их приоритеты приведены в таблице:

Разряд 7 в регистре статуса SREG.7=1 разрешает все прерывания (глобальное прерывание)

§ Для каждого типа прерываний есть локальные разрешения

прерываний, которые находятся в управляющих регистрах соответствующих устройств МК.

В среде СodeVision при формировании проекта можно выбрать прерывание от соответствующих устройства, при этом в коде программы появится секция для кода обработчика прерываний.

Список устройств, их структура и функционирование, также и назначение битов регистров, управляющих работой устройств можно изучить в русскоязычном документе ATmega128 из папки с файлами лабораторной рабты. Архитектура этого процессора во многом схожа с архитектурой процессора ATmega16.

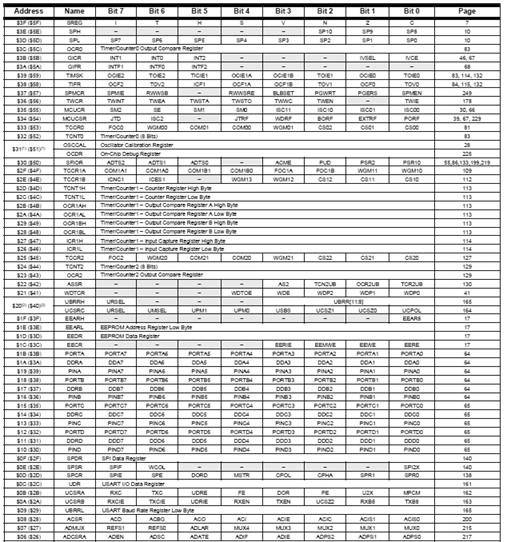

Назначение битов регистров приведено в конце документа.

Статьи к прочтению:

Easy AVR 2016 02 14Архитектура микроконтроллера AVRЧасть 1

Похожие статьи:

-

Краткое описание программы wireshark и рекомендации по работе с программой

Федеральное агентство связи Федеральное государственное образовательное бюджетное Учреждение Высшего профессионального образования Московский технический…

-

Архитектура микроконтроллера msp430f2013

На рисунке Б.1 приведена общая структурная схема микроконтроллеров семейства MSP430 [4]. Отдельные устройства подчиняются общим архитектурным принципам и…