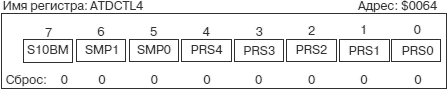

Регистр управления atdctl4формат регистра atdctl4

Рис 6. Формат регистра управления

Регистр управления ATDCTL4 располагается в памяти по адресу $0064. Формат регистра управления ATDCTL4 приведен на рис 6. Этот регистр позволяет регулировать время выборки для устройства выборки и хранения на входе АЦП последовательного приближения. Полное время преобразования 8-разрядного АЦП в составе модуля ATD складывается из четырех интервалов:

• Интервал начального запуска, состоит из 2 периодов частоты тактирования модуля ATD;

• Неизменяемый интервал выборки аналогового сигнала, состоит из 4 периодов частоты тактирования модуля ATD;

• Регулируемый интервал выборки аналогового сигнала, его длительность программируется посредством установки битов SMP1:SMP0 в регистре управления ATDCTL4;

• Интервал преобразования напряжения на выходе устройства выборки и хранения аналого-цифровым преобразователем, состоит из 10 периодов частоты тактирования модуля ATD.

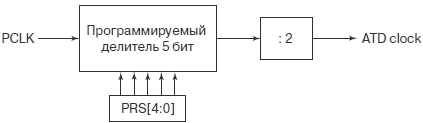

Рис. 7. Структура системы тактирования модуля ATD

Структурная схема подсистемы тактирования модуля ATD представлена на рис. 7. На вход подсистемы поступает импульсная последовательность PCLK с частотой fBUS. Эта импульсная последовательность поступает на вход программируемого делителя частоты.

Частота тактирования модуля аналого-цифрового преобразования ATDclock формируется из PCLK путем деления двумя делителями частоты. Коэффициент деления первого делителя переменный, определяется пятью битами PRS4…PRS0 регистра ATDCTL4. Численное значение коэффициента равно десятичному эквиваленту пятиразрядного двоичного кода PRS4…PRS0 плюс 1.

Например, если в разрядах PRS4…PRS0 записан код 00101b, то коэффициент деления равен шести (5+1). Коэффициент деления второго делителя равен двум. Поэтому в рассматриваемом примере частота тактирования модуля ATD составит fBUS/12.

Биты SMP1:SMP0 определяют регулируемый интервал выборки аналогового сигнала. Мы уже установили, что полное время одного аналого-цифрового преобразования равно 16 периодов частоты модуля ATD плюс регулируемый интервал выборки. На рис. 8 представлены четыре возможные комбинации кодов в разрядах SMP1:SMP0 и соответствующие им времена регулируемого интервала выборки и полного времени преобразования. Из рис. 8 следует, что минимальное время одного аналого-цифрового преобразования составляет 18 периодов, а максимальное — 32 периода частоты тактирования модуля ATD.

| SMP1:SMP0 | Время выборки (периоды ADTclock) | Полное время 8-разрядногопреобразования (периоды ADTclock) |

Рис. 8.Выбор времени аналого-цифрового преобразования в модуле ATD

Бит S10BM определяет разрядность аналого-цифрового преобразования. При S10BM=0, АЦП в составе модуля формирует 8-разрядный код измеряемого сигнала, при S10BM=1 разрядность кода равна 10.

Статьи к прочтению:

STM8 — Урок #4. Модуль тактирования. Таймер TIM4

Похожие статьи:

-

Рис. 5.Формат регистра ATDCTL2 Регистр управления ATDCTL2 располагается в памяти по адресу $0062. Этот регистр в первую очередь используется для…

-

Управление обменом в сети с топологией шина

При топологии шина также возможно централизованное управление. При этом один из абонентов ( центральный ) посылает по шине всем остальным ( периферийным…