Рхитектура мп. функции устройства управления.

4.Система команд МП

1.В основу построения МПС-систем положено три принципа:

? магистральности;

? модульности;

? микропрограммного управления.

Принцип магистральности определяет характер связей между функциональными блоками МПС — все блоки соединяются с единой системной шиной.

Принцип модульности состоит в том, что система строится на основе ограниченного количества типов конструктивно и функционально законченных модулей. Каждый модуль МПС имеет вход управления третьим (высокоимпедансным) состоянием. Этот вход называется CS (ChipSelect) — выборкристалла, или ОЕ (OutputEnable) — разрешение выхода.

Принципы магистральности и модульности позволяют наращивать управляющие и вычислительные возможности МП путем подсоединения других модулей к системной шине.

Принцип микропрограммного управления состоит в возможности осуществления элементарных операций — микрокоманд (сдвигов, пересылок информации, логических операций). Используя определенные комбинации микрокоманд, можно создать технологический язык, т. е. набор команд, который максимально соответствует назначению системы. В секционных процессорах набор микрокоманд можно изменить, используя другие микросхемы памяти микрокоманд.

Обобщенная структурная схема МПС показана на рис. 1.4. В состав МПС

входят:

? центральный процессор (ЦП);

? ПЗУ;

? ОЗУ;

? система прерываний;

? таймер;

? устройства ввода/вывода (УВВ).

Устройства ввода/вывода подключаются к системной шине через интерфейсы ввода/вывода. Под интерфейсом понимают совокупность аппаратных, программных и конструктивных средств, необходимых для реализации взаимодействия различных функциональных компонентов в системах и направленные на обеспечение информационной, электрической и конструктивной совместимости компонентов. Интерфейс должен обеспечивать простое и быстрое соединение данных устройства с любым другим, имеющим такой же интерфейс, совместную работу устройств без ухудшения их технических характеристик, высокая надежность. Основными элементами интерфейса являются: совокупность правил обмена информации (временные диаграммы и диаграммы состояний сигналов интерфейса), аппаратная реализация (физическая реализация – контроллеры), программное обеспечение интерфейса (драйверы).

Постоянное и оперативное запоминающие устройства образуют систему памяти, предназначенную для хранения информации в виде двоичных чисел. Постоянное запоминающее устройство предназначено для хранения программ управления, таблиц, констант; ОЗУ — для хранения промежуточных результатов вычислений.

Сегментом называется область памяти, которая начинается с любого адрес кратного 16, и занимает до 64 Кбайт. Существуют три основных сегмента:

? сегмент кодов;

? сегмент данных;

? сегмент стека.

Сегмент кодов содержит коды команд, которые адресуются сегментным регистром кодов CSи регистром — указателем команд IP (InstructionPointer). Регистр CSопределяет начальный адрес сегмента кодов, а регистр IP— смещение в сегменте (расстояние от начала сегмента до ячейки, в которой находится адрес команды).

Сегмент данных содержит данные, константы и рабочие области, необходимые для выполнения программы. Начальный адрес сегмента данных содержится в регистре DS, а смещение в сегменте задается командой.

Сегмент стека содержит адрес возврата из подпрограмм и данные. Регистр SSсодержит начальный адрес сегмента стека, а регистр SP— смещение в сегменте.

Модуль центрального процессора осуществляет обработку данных и управляет всеми остальными модулями системы. Центральный процессор, кроме БИС МП, содержит схемы синхронизации и интерфейса с системной шиной. Он осуществляет выборку кодов команд из памяти, дешифрует их и выполняет. В течение времени выполнения команды — командного цикла — ЦП выполняет такие действия:

1. Выставляет адрес команды на шину адреса АВ.

2. Получает код команды из памяти и дешифрует его.

3. Вычисляет адрес операнда и считывает данные.

4. Выполняет операцию, определенную командой.

5.Воспринимает внешние управляющие сигналы, например, запрос прерываний.

6.Генерирует сигналы состояния и управления, необходимые для работы памяти и УВВ.

Устройства ввода/вывода или внешние устройства — это устройства, предназначенные для ввода информации в МП или вывода информации из него. Примерами УВВ являются дисплеи, печатающие устройства, клавиатура, цифро-аналоговый и аналогово-цифровой преобразователи, реле, коммутаторы. Для соединения УВВ с системной шиной их сигналы должны соответствовать определенным стандартам, что реализуется с помощью интерфейсов ввода/вывода.

Интерфейсы ввода/вывода называют также контроллерами или адаптерами. Микропроцессор обращается к интерфейсам с помощью специальных команд ввода/вывода. При этом МП выставляет на шину адреса АВ адрес интерфейса, а по шине данных DBсчитывает данные с устройства ввода или записывает в устройство вывода.

Система прерываний позволяет МПС реагировать на внешние сигналы — запросы прерываний, источниками которых могут быть: сигналы готовности от внешних устройств, сигналы от генераторов, сигналы с выходов датчиков. При появлении запроса на прерывание ЦП прекращает выполнение основной программы и переходит к выполнению подпрограммы обслуживания запроса прерывания. Для построения системы прерываний МПК содержат БИС специальных программируемых контроллеров прерываний.

Таймер предназначен для реализации функций, связанных с отсчетом времени. После того как МП загружает в таймер число, задающее частоту, задержку или коэффициент деления, таймер реализует необходимую функцию.

2.Понятие архитектуры микропроцессора определяет его составные части, а также связи и взаимодействие между ними. Архитектура включает:

? структурную схему МП;

? программную модель МП (описание функций регистров);

?информацию об организации памяти (емкость и способы адресации памяти);

? описание организации процедур ввода/вывода.

Классификация архитектур ЭВМ возможна по ряду признаков, например по: изолированности адресных пространств, количеству процессоров, количеству одновременно обрабатываемых потоков команд и данных, по системам команд и т.д.

По количеству и скорости выполнения команд различают CISC- и RISC-архитектуры.

Архитектура СISC(ComplexInstructionSetCommand) – с полным набором команд. Данная архитектура отличается большим числом разнообразных команд; переменной длиной команд; значительным числом способов адресации и форматов команд; сложностью команд и многотактностью их выполнения; наличием микропрограммного управления. Все это снижает быстродействие и усложняет процессор, но облегчает процесс написания программ..

Архитектура RISC(ReducedInstructionSetCommand) – с сокращенным набором команд. Данная архитектура большинство команд выполняет за один машинный такт; длина команд постоянна; имеется небольшое количество способов адресации и форматов команд; для простых команд нет необходимости в использовании микропрограммного управления; имеется большое число регистров процессора. ЭВМ RISC архитектуры более быстрые в сравнении с CISC архитектурой.

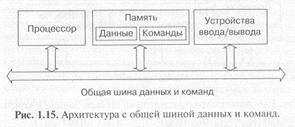

Существуют два основных типа архитектуры — фоннеймановская и гарвардская. Фоннеймановскую архитектуру (рис. 1.15) предложил в 1945 году американский математик Джо фон Нейман. Особенностью этой архитектуры является то, что программа и данные находятся в общей памяти, доступ к которой осуществляется по одной шине данных и команд. Пример: классические ЭВМ, такие как обычные персональные компьютеры, в которых программы и данные расположены в едином ОЗУ.

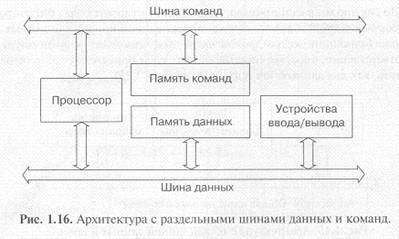

Гарвардская архитектура впервые была реализована в 1944 году в релейной вычислительной машине Гарвардского университета (США). Особенностью этой архитектуры является то, что память данных и память программ разделены и имеют отдельные шину данных и шину команд (рис. 1.16), что позволяет повысить быстродействие МП системы. Программа в таких системах обычно хранится в ПЗУ требуемого объема, и допускает только чтение, а данные расположены в ОЗУ, работающем в режимах чтения и записи информации. Пример: большинство микроконтроллеров (МК) и однокристальных ЭВМ (ОЭВМ).

Архитектура с общей шиной распространена гораздо больше, она применяется, например, в персональных компьютерах и в сложных микро компьютерах. Архитектура с раздельными шинами применяется в основном в однокристальных микроконтроллерах.

Рассмотрим некоторые достоинства и недостатки обоих архитектурных решений.

Архитектура с общей шиной (принстонская, фон-неймановская) проще, она не требует от процессора одновременного обслуживания двух шин, контроля обмена по двум шинам сразу. Наличие единой памяти данных и команд позволяет гибко распределять ее объем между кодами данных и команд. Например, в некоторых случаях нужна большая и сложная программа, а данных в памяти надо хранить не слишком много. В других случаях, наоборот, программа требуется простая, но необходимы большие объемы хранимых данных. Перераспределение памяти не вызывает никаких проблем, главное — чтобы программа и данные вместе помещались в памяти системы. Какправило, в системах с такой архитектурой память бывает довольно большого объема. Это позволяет решать самые сложные задачи.

Архитектура с раздельными шинами данных и команд сложнее, она заставляет процессор работать одновременно с двумя потоками кодов, обслуживать обмен по двум шинам одновременно. Программа может размещаться только в памяти команд, данные — только в памяти данных. Такая узкая специализация ограничивает круг задач, решаемых системой, так как не дает возможности гибкого перераспределения памяти.Память данных и память команд в этом случае имеют не слишком большой объем, поэтому применение систем с данной архитектурой ограничивается обычно не слишком сложными задачами.

В чем же преимущество архитектуры с двумя шинами (гарвардской)? В первую очередь, в быстродействии.

Дело в том, что при единственной шине команд и данных процессор вынужден по одной этой шине принимать данные (из памяти или устройства ввода/вывода) и передавать данные (в память или в устройство ввода/ вывода), а также читать команды из памяти. Естественно, одновременно эти пересылки кодов по магистрали происходить не могут, они должны производиться по очереди. Современные процессоры способны совместить во времени выполнение команд и проведение циклов обмена по системной шине. Использование конвейерных технологий и быстрой кэш памяти позволяет им ускорить процесс взаимодействия со сравнительно медленной системной памятью. Повышение тактовой частоты и совершенствование структуры процессоров дают возможность сократить время выполнения команд. Но дальнейшее увеличение быстродействия системы возможно только при совмещении пересылки данных и чтения команд, то есть при переходе к архитектуре с двумя шинами.

В случае двухшинной архитектуры обмен по обеим шинам может быть независимым, параллельным во времени. Соответственно, структуры шин (количество разрядов кода адреса и кода данных, порядок и скорость обмена информацией и т.д.) могут быть выбраны оптимально для той задачи, которая решается каждой шиной. Поэтому при прочих равных условиях переход на двухшинную архитектуру ускоряет работу микропроцессорной системы, хотя и требует дополнительных затрат на аппаратуру, усложнения структуры процессора. Память данных в этом случае имеет свое распределение адресов, а память команд — свое.

Проще всего преимущества двухшинной архитектуры реализуются внутри одной микросхемы. В этом случае можно также существенно уменьшить влияние недостатков этой архитектуры. Поэтому основное ее применение — в микроконтроллерах, от которых не требуется решения слишком сложных задач, но зато необходимо максимальное быстродействие при заданной тактовой частоте.

3.Структурные схемы обоих типов архитектур содержат: процессорный элемент, память, интерфейсы ввода/вывода (ИВВ) и УВВ.

Память и ИВВ для разных типов МП могут быть как внутренними, т. е. размещаться на том же кристалле, что и процессорный элемент, так и внешними. Процессорный элемент содержит регистры, арифметико-логическое устройство (АЛУ), устройство управления и выполняет функции обработки данных и управления процессами обмена информацией. Память обеспечивает хранение данных и кодов команд программы. Интерфейсы ввода/вывода предназначены для связи с УВВ, например, с клавиатурой, дисплеем, печатающими устройствами, датчиками. Все элементы структурной схемы соединены с помощью шин.

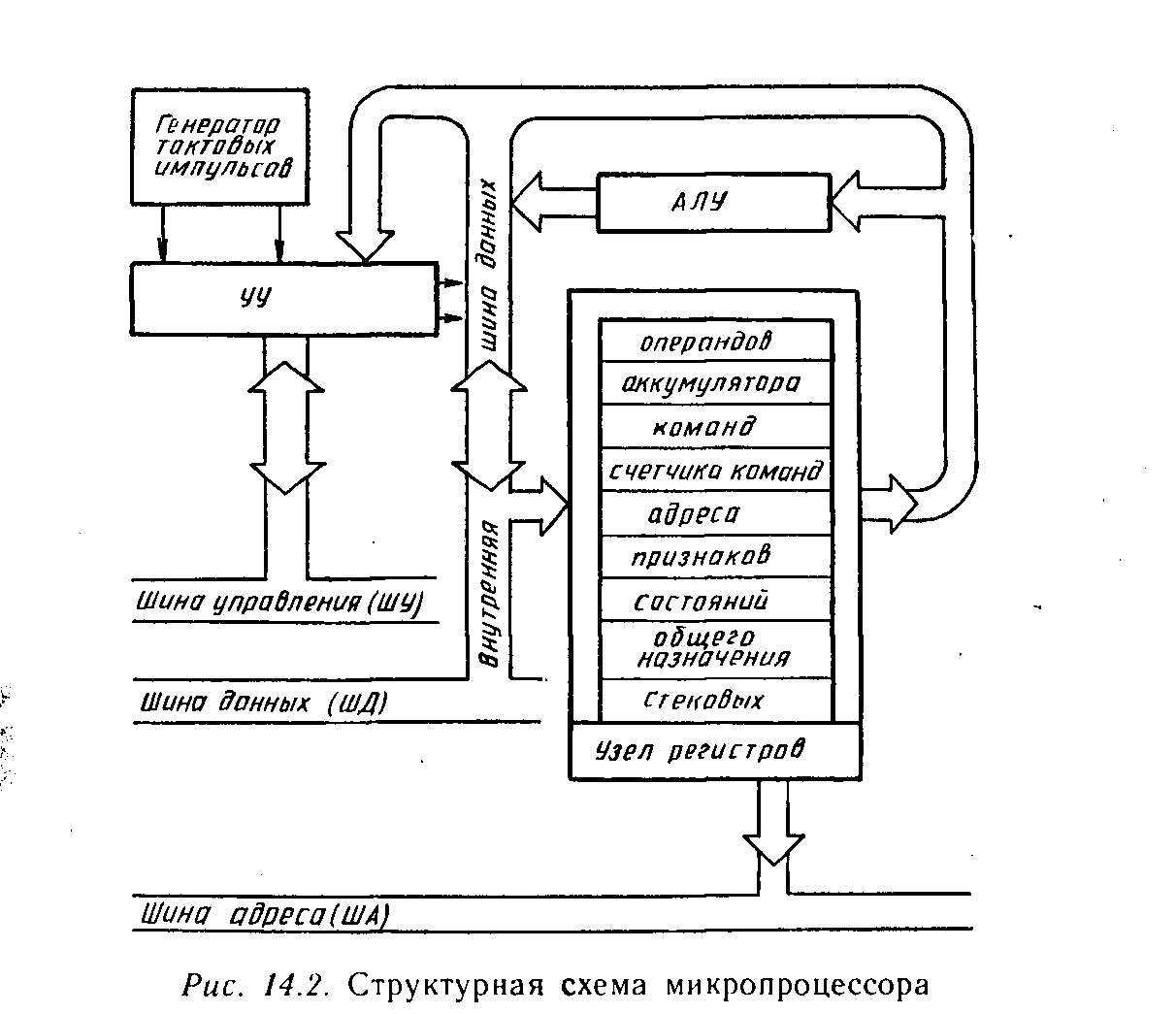

СтруктурнаясхемаМПпоказананарис.14.2.Микропроцессорвключаеттри основных узла: АЛУ,УУиузел регистров.Дляосуществлениясвязимеждуэтимиузлами используетсявнутренняя шина данных. Онасостоитиз восьми(длявосьмиразрядногоМП)линий,покоторым передаются8-разрядныеслова(байты)икомандная информация.Передачасловповнутреннейшинеданных междуузламиМПосуществляетсявобоихнаправлениях, новразныенепересекающиесявременныеинтервалы.

Основнаячасть,илиядро,МП—этоАЛУ,осуществляющееобработкуданных.Типичнымиоперациями,

выполняемымиАЛУ,являютсясложение,вычитание,логическоесложение(ИЛИ),логическоеумножение(И), сложениепомодулю2(ИСКЛЮЧАЮЩЕЕИЛИ),инверсия,сдвиг,пересылка.ОбычноАЛУимеетдвавхода, которыеназываютсявходнымипортами,иодинвыход, иливыходнойпорт.ДанныенавходныепортыАЛУпоступаютсвнутреннейшиныданныхилиизспециального регистра,называемогоаккумулятором,черезбуферные регистры,илирегистрыоперандов,предназначенныедля временногохраненияданных. Таким образом, АЛУ выполняет арифметические или логические операции над операндами, которые пересылаются из памяти и/или регистров МП. Операнд — это объект в виде значения данных, содержимого регистров или содержимого ячейки памяти, с которым оперирует команда. Например, в команде сложения операндами являются слагаемые. Операнд может задаваться в команде в виде числа либо находиться в регистре или ячейке памяти. Полученный после выполнения команды в АЛУ результат пересылается в регистр или ячейку памяти.

Регистры предназначены для хранения n-разрядного двоичного числа. Они представляют собой n триггеров со схемами управления чтением/записью и выборки. Регистры создают внутреннюю память МП и используются для хранения промежуточных результатов вычислений.

Любая задача решается по программе, которая представляет собой строгую последовательность нужных команд. Эту последовательность поступления команд обеспечивает регистр, называемый счетчиком команд. Онявляется адресным регистром, указывающим на адрес ячейки памяти в пространстве памяти программ, хранящей код команды, которая будет выполнена следом за текущей командой.

Счетчик команд может иметь большее число разрядов, чем длина слова данных. В результате можно записать команду в любую ячейку памяти.

Перед выполнением программы в счетчик команд записывают число, которое определяет адрес первой программы, хранящейся в ЗУ. Затем это число из счетчика команд переписывается в 16-разрядный регистр адреса памяти. Из регистра адреса памяти по шине адреса (ША) адрес первой команды посылается в устройство управления памятью. По указанному адресу из ЗУ осуществляется считывание первой команды, которая переписывается в регистр команд.

Рассмотренный цикл операций называют циклом выборки или фазой адресации.

Аккумулятор — это регистр, в котором хранится один из операндов. После выполнения команды в аккумуляторе вместо операнда размещается результат операции. В 8-разрядных процессорах аккумулятор принимает участие во всех операциях АЛУ. В 16-разрядных МП большинство команд выполняется без участия аккумулятора, однако в некоторых командах (ввод, вывод, умножение, деление) аккумулятор действует так же, как и в 8-разрядных МП, т. е. сохраняет один из операндов, а после выполнения команды — результат операции.

Регистркоманд предназначен для хранения кода операции текущей выполняемой команды. Данный регистр недоступен для программиста. Данные в него поступают автоматически по шине данных во время фазы выборки команды из памяти.

Регистр признаков, или флажковый регистр, служит для индикации различных признаков результатов операций, выполняемых АЛУ: нулевого результата, переполнения и др. Он состоит из отдельных триггеров, называемых флажками, которые в зависимости от проявления того или иного признака устанавливаются в состоянии О или 1. Эта информация необходима программисту при составлении и отладке программы вычислений.

Регистр состояний воспринимает информацию из ре гистра признаков и в зависимости от значений признаков позволяет изменять последовательность выполнения команд и осуществлять так называемые условные переходы. При этом изменяется содержание счетчика команди он настраивается на выборку не следующей, а нужной команды. Наличие команд условного перехода делает МП более универсальным, позволяет выбирать различные пути решения задачи в зависимости от возникающих в ходе решения условий.

Регистр операндов предназначен для хранения операндов на время выполнения над ними операций в АЛУ. Они не доступны программисту для использования.

Регистры общего назначения используются в качестве запоминающих устройств промежуточных результатов вычислений, адресов и команд, а иногда и в качестве аккумуляторов. Число таких регистров в МП может доходить до 16., причем разрядность их может быть различной. Отдельные регистры общего назначения могут соединяться между собой последовательно и рассматриваться как один регистр с большим числом разрядов.

Особую группу составляют стековые регистры, подразделяющиеся на регистры стека и указатель стека. Эти регистры позволяют без обмена с ЗУ организовать необходимую последовательность выполнения команд, например последовательность выполнения по старшинству различных арифметических действий. Стековые регистры подключены таким образом, что первая команда, записанная в первый регистр, при записи второй команды «проталкивается» во второй регистр, а в первом оказывается записанной вторая команда. При записи третьей команды первая переходит в третий регистр, вторая — во второй и т. д. При выборке команд из стека первой выбирается последняя, затем предпоследняя и т. Д

Количество регистров (глубина) стека является важной характеристикой МП. Для увеличения глубины стека его часто организуют в некоторой области внешнего ЗУ.

Указатель стека определяет адрес ячейки (регистра) стека, заполненной последней командой. Эта ячейка называется вершиной стека. После выборки команды из стека содержимое указателя стека уменьшается на 1, а при записи в стек очередной команды — увеличивается на 1.

РаботойАЛУивнутреннимирегистрамиуправляетУУ,котороеизвлекаетизрегистракомандочередную команду, дешифрирует ее,т.е.определяет,какая операция должна осуществляться,иобеспечиваетвыполнение этой операции в АЛУ.

После записи команды в регистр УУ осуществляет ее распознавание (декодирование), и в АЛУ поступают сигналы, стимулирующие выполнение данной команды. Этот процесс называют циклом или фазой выполнения команды.

Устройство управления вырабатывает управляющие сигналы для всех блоков структурной схемы МП в соответствии с кодами команд, внешними управляющими сигналами и сигналами синхронизации, а также управляет обменом информацией между МП, памятью и УВВ. Устройство управления реализует такие функции: начальная установка МП, синхронизация, прерывания, согласование быстродействия модулей МПС.

Функция начальной установки МП. Внешний сигнал начальной установки процессора RESETформируется при включении источника питания МП или при нажатии кнопки RESET. При появлении этого сигнала устройство управления обеспечивает загрузку нулевого значения в указатель команд, который инициирует выборку из памяти байта команды с нулевым адресом. В конце выборки содержимое указателя команд увеличивается на единицу, и выбирается байт команды со следующим адресом. Таким образом выполняется вся записанная в памяти программа.

Функции синхронизации. В соответствии с внешними управляющими сигналами и сигналами синхронизации устройство управления синхронизирует работу всех блоков МП.

Функция прерываний. С поступлением сигнала прерывания устройство управления инициирует выполнение подпрограммы обработки соответствующего прерывания. Потребность в реализации функций прерываний возникает тогда, когда во время выполнения основной программы надо перевести МП на решение другой задачи, например, обработки аварийной ситуации или работы с УВВ.

Функция согласования быстродействия модулей микропроцессорной системы. Во время обслуживания памяти и УВВ, быстродействие которых значительно меньше, чем у МП, согласование быстродействия реализуется генерацией тактов ожидания МП. Во время обслуживания устройств с большим быстродействием, чем у МП, используется режим прямого доступа к памяти.

Цикл выборки совместно с циклом выполнения команды образуют цикл команды.

Взаимодействие и координация работы всех узлов микропроцессорной системы осуществляется высокостабильным генератором тактовых импульсов, с помощью которых формируются машинные циклы и циклы команд. Машинным циклом называют время, требуемое для извлечения одного байта информации из памяти или выполнения команды, определяемой одним машинным словом

4.Программа представляет собой последовательность команд, выполнение которых приводит к решению задачи.

Команда определяет операцию, которую выполняет МП над данными. Команда содержит в явной или неявной форме информацию о том, где будет помещен результат операции, а также об адресе следующей команды. Код команды состоит из нескольких частей, которые называются полями. Состав, назначение и расположение полей называется форматом команды. В общем случае формат команды содержит операционную и адресную части. Операционная часть содержит код операции (например, сложение, умножение, передача данных). Адресная часть состоит из нескольких полей и содержит информацию об адресах операндов, результата операции и следующей команды.

Набор команд, выполняемых МП, делятся на ряд групп, основными из которых являются команды арифметических и логических операций, пересылок, ввода-вывода, управления, обращения к подпрограмме и некоторые специальные команды.

Команды арифметических и логических операций обеспечивают выполнение операций арифметического сложения, вычитания и умножения двоичных и двоично-десятичных чисел, их сравнение, а также выполнение операций логического сложения, логического умножения, сложение по модулю 2, инверсию чисел и др. После выполнения этих команд результат операции поступает в аккумулятор или в указанную в этих командах ячейку ЗУ.

Арифметические команды рассматривают коды операндов как числовые двоичные или двоично-десятичные коды. Эти команды могут быть разделены на пять основных групп:

— команды операций с фиксированной запятой (сложение, вычитание, умножение, деление);

— команды операций с плавающей запятой (сложение, вычитание, умножение, деление);

— команды очистки;

— команды инкремента и декремента;

— команда сравнения.

Команды операций с фиксированной запятой работают с кодами в регистрах процессора или в памяти как с обычными двоичными кодами. Команда сложения (ADD) вычисляет сумму двух кодов. Команда вычитания (SUB) вычисляет разность двух кодов. Команда умножения (MUL) вычисляет произведение двух кодов (разрядность результата вдвое больше разрядности сомножителей). Команда деления (DIV) вычисляет частное от деления одного кода на другой. Причем все эти команды могут работать как с числами со знаком, так и с числами без знака.

Команды операций с плавающей запятой (точкой) используют формат представления чисел с порядком и мантиссой (обычно эти числа занимают две последовательные ячейки памяти). В современных мощных процессорах набор команд с плавающей запятой не ограничивается только четырьмя арифметическими действиями, а содержит и множество других более сложных команд, например, вычисление тригонометрических функций, логарифмических функций, а также сложных функций, необходимых при обработке звука и изображения.

Команды очистки (CLR) предназначены для записи нулевого кода в регистр или ячейку памяти. Эти команды могут быть заменены командами пересылки нулевого кода, но специальные команды очистки обычно выполняются быстрее, чем команды пересылки. Команды очистки иногда относят к группе логических команд, но суть их от этого не меняется.

Команды инкремента (увеличения на единицу, INC) и декремента (уменьшения на единицу, DEC) также бывают очень удобны. Их можно в принципе заменить командами суммирования с единицей или вычитания единицы, но инкремент и декремент выполняются быстрее, чем суммирование и вычитание. Эти команды требуют одного входного операнда, который одновременно является и выходным операндом.

Команда сравнения (обозначается CMP) предназначена для сравнения двух входных операндов. По сути, она вычисляет разность этих двух операндов, но выходного операнда не формирует, а всего лишь изменяет биты в регистре состояния процессора (PSW) по результату этого вычитания. Следующая за командой сравнения команда (обычно это команда перехода) будет анализировать биты в регистре состояния процессора и выполнять действия в зависимости от их значений (о командах перехода речь идет в разделе 3.3.4). В некоторых процессорах предусмотрены команды цепочечного сравнения двух последовательностей операндов, находящихся в памяти (например, в процессоре 8086 и совместимых с ним).

CMPS –сравнение символов строки.

Логические команды выполняют над операндами логические (побитовые) операции, то есть они рассматривают коды операндов не как единое число, а как набор отдельных битов. Этим они отличаются от арифметических команд. Логические команды выполняют следующие основные операции:

— логическое И, логическое ИЛИ, сложение по модулю 2 (Исключающее ИЛИ);

— логические, арифметические и циклические сдвиги;

— проверка битов и операндов;

— установка и очистка битов (флагов) регистра состояния процессора (PSW).

Команды логических операций позволяют побитно вычислять основные логические функции от двух входных операндов. Кроме того, операция И (AND) используется для принудительной очистки заданных битов (в качестве одного из операндов при этом используется код маски, в котором разряды, требующие очистки, установлены в нуль). Операция ИЛИ (OR) применяется для принудительной установки заданных битов (в качестве одного из операндов при этом используется код маски, в котором разряды, требующие установки в единицу, равны единице). Операция «Исключающее ИЛИ» (XOR) используется для инверсии заданных битов (в качестве одного из операндов при этом применяется код маски, в котором биты, подлежащие инверсии, установлены в единицу). Команды требуют двух входных операндов и формируют один выходной операнд.

Команды сдвигов позволяют побитно сдвигать код операнда вправо (в сторону младших разрядов) или влево (в сторону старших разрядов). Тип сдвига (логический, арифметический или циклический) определяет, каково будет новое значение старшего бита (при сдвиге вправо) или младшего бита (при сдвиге влево), а также определяет, будет ли где-то сохранено прежнее значение старшего бита (при сдвиге влево) или младшего бита (при сдвиге вправо). Циклические сдвиги позволяют сдвигать биты кода операнда по кругу (по часовой стрелке при сдвиге вправо или против часовой стрелки при сдвиге влево). При этом в кольцо сдвига может входить или не входить флаг переноса.

RCL- циклический сдвиг влево

RCR- циклический сдвиг вправо

SAL- арифметический сдвиг влево

SAR-арифметический сдвиг вправо

Команды проверки битов и операндов предназначены для установки или очистки битов регистра состояния процессора в зависимости от значения выбранных битов или всего операнда в целом. Выходного операнда команды не формируют. Команда проверки операнда (TST) проверяет весь код операнда в целом на равенство нулю и на знак (на значение старшего бита), она требует только одного входного операнда. Команда проверки бита (BIT) проверяет только отдельные биты, для выбора которых в качестве второго операнда используется код маски.

Команды установки и очистки битов регистра состояния процессора (то есть флагов) позволяют установить или очистить любой флаг, что бывает очень удобно. Каждому флагу обычно соответствуют две команды, одна из которых устанавливает его в единицу, а другая сбрасывает в нуль. Например, флагу переноса C (от Carry) будут соответствовать команды CLC (очистка) и SEC или STC (установка).

Команды пересылок используются для осуществления пересылки данных из одной ячейки ЗУ в другую, в аккумулятор или наоборот. К ним относятся команды загрузки регистра, регистровой пары и аккумулятора, пересылки из регистра в регистр, записи содержимого аккумулятора в память. Их основные функции: загрузка (запись) содержимого во внутренние регистры процессора; сохранение в памяти содержимого внутренних регистров процессора; копирование содержимого из одной области памяти в другую; запись в устройства ввода/вывода и чтение из устройств ввода/вывода.

В некоторых процессора все эти функции выполняются одной единственной командой MOV (для байтовых пересылок — MOVB), но с различными методами адресации операндов.

В других процессорах помимо команды MOV имеется еще несколько команд для выполнения перечисленных функций. Например, для загрузки регистров могут использоваться команды загрузки, причем для разных регистров — разные команды (их обозначения обычно строятся с использованием слова LOAD — загрузка). Часто выделяются специальные команды для сохранения в стеке и для извлечения из стека (PUSH — сохранить в стеке, POP — извлечь из стека).

Иногда в систему команд вводится специальная команда MOVS для строчной (или цепочечной) пересылки данных (например, в процессоре 8086). Эта команда пересылает не одно слово или байт, а заданное количество слов или байтов (MOVSB), то есть инициирует не один цикл обмена по магистрали, а несколько. При этом адрес памяти, с которым происходит взаимодействие, увеличивается на 1 или на 2 после каждого обращения или же уменьшается на 1 или на 2 после каждого обращения.

Также к командам пересылки данных относятся команды обмена информацией (их обозначение строится на основе слова Exchange). Может быть предусмотрен обмен информацией между внутренними регистрами, между двумя половинами одного регистра (SWAP) или между регистром и ячейкой памяти.

Команды ввода-вывода служат для введения через шину данных входной информации, представленной в двоичном коде, в аккумулятор МП или для вывода содержимого аккумулятора на устройство отображения информации. В некоторых процессорах (например, в процессоре 8086) специально выделяются функции обмена с устройствами ввода/вывода. Команда IN используется для ввода (чтения) информации из устройства ввода/вывода, а команда OUT используется для вывода (записи) в устройство ввода/вывода. Обмен информацией в этом случае производится между регистром-аккумулятором и устройством ввода/вывода. В более продвинутых процессорах этого же семейства (начиная с процессора 80286) добавлены команды строчного (цепочечного) ввода (команда INS) и строчного вывода (команда OUTS). Эти команды позволяют пересылать целый массив (строку) данных из памяти в устройство ввода/вывода (OUTS) или из устройства ввода/вывода в память (INS). Адрес памяти после каждого обращения увеличивается или уменьшается (как и в случае с командой MOVS).

Команды управления включают в себя команды безусловных и условных переходов. По этим командам изменяется содержимое счетчика команд и нарушается последовательность выполнения команд программы.

При безусловном переходе нарушение последовательности выполнения программы происходит всякий раз при выполнении программы. При этом адрес ячейки, в которой хранится команда и к которой осуществляется переход, содержится в адресной части команды, по которой осуществляется этот переход.

При условных переходах последовательность выполнения команд программы нарушается лишь в том случае, когда результат вычислений, предусмотренных программой, удовлетворяет некоторому поставленному условию. В качестве таких условий обычно выступают значения флагов в регистре состояния процессора (PSW). То есть условием перехода является результат предыдущей операции, меняющей значения флагов. Всего таких условий перехода может быть от 4 до 16. Несколько примеров команд условных переходов:

— переход, если равно нулю (JE);

— переход, если не равно нулю (JNE);

— переход, если есть переполнение (JO);

— переход, если нет переполнения (JNO);

— переход, если больше нуля (JG);

— переход, если меньше или равно нулю(JLE).

JMP- безусловный переход.

Если условие перехода выполняется, то производится загрузка в регистр-счетчик команд нового значения. Если же условие перехода не выполняется, счетчик команд просто наращивается, и процессор выбирает и выполняет следующую по порядку команду.

Специально для проверки условий перехода применяется команда сравнения (CMP), предшествующая команде условного перехода (или даже нескольким командам условных переходов). Но флаги могут устанавливаться и любой другой командой, например командой пересылки данных, любой арифметической или логической командой. Отметим, что сами команды переходов флаги не меняют, что как раз и позволяет ставить несколько команд переходов одну за другой

Команды обращения к подпрограмме являются разновидностями команд управления. Обычно подпрограммы хранятся в регистрах стека, которые в большинстве случаев размещаются в ЗУ. При обращении к подпрограмме вначале происходит запоминание текущего содержания счетчика команд. Затем в счетчик записывается адрес 1-ой команды подпрограммы. Последней командой подпрограммы является команда «Возврат из подпрограммы», по которой в счетчике восстанавливается число, соответствующее прерванной команде основной программы. По команде «Возврат из подпрограммы» может также осуществляться переход из одной подпрограммы к другой, если используется вложение подпрограмм.

CALL- вызов подпрограммы.

Для обратного возврата в точку вызова подпрограммы (точку перехода) используется специальная команда возврата (RET или RTS). Эта команда извлекает из стека значение адреса команды перехода и записывает его в регистр-счетчик команд.

Особую форму подпрограммы составляет операция, называемая прерыванием. Она заключается в том, что прекращение действий текущей программы осуществляется произвольно по запросу внешнего управляющего сигнала. Особое место среди команд перехода с возвратом занимают команды прерываний (распространенное название — INT). Эти команды в качестве входного операнда требуют номер прерывания (адрес вектора). Обслуживание таких переходов осуществляется точно так же, как и аппаратных прерываний. То есть для выполнения данного перехода процессор обращается к таблице векторов прерываний и получает из нее по номеру прерывания адрес памяти, в который ему необходимо перейти. Адрес вызова прерывания и содержимое регистра состояния процессора (PSW) сохраняются в стеке. Сохранение PSW — важное отличие команд прерывания от команд переходов с возвратом.

INTO-прерывание при переполнении.

Команды прерываний во многих случаях оказываются удобнее, чем обычные команды переходов с возвратом. Сформировать таблицу векторов прерываний можно один раз, а потом уже обращаться к ней по мере необходимости. Номер прерывания соответствует номеру подпрограммы, то есть номеру функции, выполняемой подпрограммой. Поэтому команды прерывания гораздо чаще включаются в системы команд процессоров, чем обычные команды переходов с возвратом.

Для возврата из подпрограммы, вызванной командой прерывания, используется команда возврата из прерывания (IRET или RTI). Эта команда извлекает из стека сохраненное там значение счетчика команд и регистра состояния процессора (PSW).

К специальным командамотносятся команды разрешения прерывания, запрещения прерывания, остановка и холостая операция. При исполнении команды «Холостая операция» никакие операции не выполняются, а содержимое счетчика адресов увеличивается на 1, после чего выполняется следующая по порядку команда.

NOP- отсутствие операции

HLT- остановка.

Статьи к прочтению:

Устройство процессора

Похожие статьи:

-

Функции устройств ввода/вывода

Устройства ввода/вывода обмениваются информацией с магистралью по тем же принципам, что и память. Наиболее существенное отличие с точки зрения…

-

Функции процессора Процессор (рис. 3.1) обычно представляет собой отдельную микросхему или же часть микросхемы (в случае микроконтроллера). В прежние…