Организация памяти микроконтроллеров семейства msp430

Ю.Р. Никитин,

П.В. Лекомцев

Изучение способов адресации микроконтроллера MSP430F2013

Методические указания к выполнению лабораторной работы № 2

по дисциплине «Микропроцессорная техника» для студентов направлений 150900.62 «Технология, оборудование и автоматизация машиностроительных производств», 220100.62 «Системный анализ и управление», 221000.62 «Мехатроника и робототехника»

Ижевск 2012

УДК 004.416(07)

ББК 32.973.26-04

Н62

Рассмотрено и одобрено на заседании кафедры «Мехатронные системы» (протокол № 9 от 06.06.2012)

Рецензент: канд. техн. наук, доцент кафедры «Мехатронные системы» С.А.Трефилов

Никитин Ю.Р., Лекомцев П.В.

Изучение способов адресации микроконтроллера MSP430F2013: Методические указания к выполнению лабораторной работы № 2 по дисциплине «Микропроцессорная техника» для студентов направлений 150900.62 «Технология, оборудование и автоматизация машиностроительных производств», 220100.62 «Системный анализ и управление», 221000.62 «Мехатроника и робототехника». – Ижевск, База учебно-методических материалов ИжГТУ, 2012. – 24 с. Регистрационный номер / , кБ.

Данные методические указания к выполнению лабораторной работы № 2 по дисциплине «Микропроцессорная техника» предназначены для студентов направлений 150900.62 «Технология, оборудование и автоматизация машиностроительных производств», 220100.62 «Системный анализ и управление», 221000.62 «Мехатроника и робототехника».

В методических указаниях приведен порядок выполнения работы в интегрированной среде разработки IAR Embedded Workbench for MSP430, рассмотрены архитектура, режимы адресации и система команд центрального процессорного устройства MSP430, индивидуальные задания студентам, пример текста программы на ассемблере.

a Ю.Р.Никитин, П.В.Лекомцев 2012

Содержание

Введение. 4

Задание. 4

1 Порядок выполнения работы.. 4

2 Структура и содержание отчета. 5

3 Контрольные вопросы для защиты лабораторной работы.. 5

Литература. 5

Приложение А Варианты индивидуальных заданий. 6

Приложение Б Архитектура ЦПУ MSP430. 7

Приложение В Организация памяти микроконтроллеров семейства MSP430. 10

Приложение Г Способы адресации операндов в памяти микроконтроллеров семейства MSP430. 12

Приложение Д Форматы команд ЦПУ микроконтроллеров семейства MSP430. 17

Приложение Е Список ассемблерных команд ЦПУ микроконтроллеров семейства MSP430. 21

Приложение Ж Исходный текст программы работы с элементами массива на ассемблере. 23

Введение

Производительность микроконтроллера во многом определяется его центральным процессорным устройством (ЦПУ). Микроконтроллеры MSP430 имеют 16-битное ЦПУ, обладающего рядом возможностей, специально предназначенных для поддержки современных методов программирования, таких как вычисляемые переходы, табличные вычисления, а также использование языков высокого уровня, в частности, языка Си. Центральный процессор может адресовать память во всём диапазоне адресов без разбиения её на страницы.

В рамках данной лабораторной работы предусмотрено изучение архитектуры ЦПУ MSP430, организации памяти, способов адресации и системы команд микроконтроллеров MSP430.

Задание

1. Изучить архитектуру ЦПУ, организацию памяти, способы адресации и систему команд микроконтроллера MSP430.

2. Создать проект в интегрированной среде разработки IAR Embedded Workbench, настроить его опции.

3. Загрузить в проект тестовую программу, откомпилировать и выполнить отладку.

4. Выполнить индивидуальное задание: разработать алгоритм и программу работы с элементами массива. Варианты индивидуальных заданий представлены в приложении А.

5. Оформить отчет по лабораторной работе.

Порядок выполнения работы

Выполнение лабораторной работы состоит из следующих шагов.

Шаг 1 – создание проекта в интегрированной среде разработки IAR Embedded Workbench, настройка его опций. Данный процесс подробно описан в [1].

Шаг 2 – добавление к проекту файлов. Создайте текстовый файл с текстом тестовой программы (Приложение Г) и сохраните его с расширением .s43 или .asm. Добавьте данный файл к созданному проекту.

Шаг 3 – компиляция проекта. В основном меню для компиляции и компоновки исходных файлов Вашего проекта выберите пункт меню «ProjectRebuild All». В случае успешной компиляции можно запускать программу в отладчике.

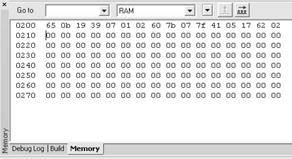

Шаг 4 – отладка. Для запуска отладчика C-SPY выберите пункт меню «ProjectDebug». Отладчик С-SPY очистит флэш-память устройства и запишет в него объектный файл Вашего приложения. Для запуска приложения выберите пункт меню «DebugGo», затем «DebugBreak». Для отображения результата работы программы выберите пункт меню «ViewMemory», элементы полученного массива в шестнадцатеричном представлении расположены в памяти по адресу 0x200 (рисунок 1).

Рисунок 1 – Дамп памяти микроконтроллера после выполнения тестовой программы

Шаг 5 – изменение текста программы в соответствии с индивидуальным заданием. Разработайте алгоритм и программу на языке ассемблер в соответствии с индивидуальным заданием. В помощь используйте краткое описание ассемблерных команд ЦПУ MSP430 (Приложение Д) и справочное руководство [5].

Структура и содержание отчета

В соответствии с заданием после выполнения лабораторной работы необходимо оформить и представить к защите отчет, содержащий следующие элементы и разделы:

— титульный лист;

— содержание;

— введение;

— задание на лабораторную работу;

— разработка схемы алгоритма решения задачи в соответствии с ГОСТ 19.701-90;

— разработка программы в соответствии с ГОСТ 19.401-78;

— результаты вычислительного эксперимента;

— выводы;

— список литературы (в соответствии с ГОСТ 7.0.5-2008).

Контрольные вопросы для защиты лабораторной работы

Для успешной защиты лабораторной работы необходимо ответить на следующие контрольные вопросы преподавателя по теме выполненной работы:

— архитектура ЦПУ MSP430;

— организация памяти микроконтроллеров семейства MSP430;

— способы адресации операндов в памяти;

— форматы команд.

Литература

1. Никитин Ю.Р., Лекомцев П.В. Изучение микроконтроллера MSP430F2013 и адаптера eZ430-F2013: Методические указания к выполнению лабораторной работы № 1 по дисциплине «Микропроцессорная техника» для студентов направлений 150900.62 «Технология, оборудование и автоматизация машиностроительных производств» и 220100.62 «Системный анализ и управление». – Ижевск, База учебно-методических материалов ИжГТУ, 2011. – 24 с.

2. MSP430x2xx Family User’s Guide (SLAU144F) – руководство пользователя на англ.яз., 2010. URL: http://ti.com (дата обращения – декабрь 2010 г.)

3. Семейство микроконтроллеров MSP430x1xx. Руководство пользователя: Пер. с англ. – М.:Серия «Библиотека Компэла». ЗАО «Компэл», 2004. – 368 с. ISBN 5-98730-001-0

4. Семейство микроконтроллеров MSP430x2xx. Архитектура, программирование, разработка приложений / пер. с англ. Евстифеева А.В. – М.: Додэка-XXI, 2010. – 544 с. ISBN 978-5-94120-221-9

5. MSP430 IAR Assembler Reference Guide (Part number: A430-3) – справочное руководство по применению языка ассемблер в среде разработки IAR для микроконтроллеров MSP430 на англ.яз., Third edition: October 2011. URL: http://netstorage.iar.com/SuppDB/Public/UPDINFO/006220/EW430_AssemblerReference.pdf (дата обращения – август 2012г.)

Приложение А

(обязательное)

Варианты индивидуальных заданий

Разработать алгоритм и программу на языке ассемблер:

1. Нахождения максимального элемента в массиве из 16 байт.

2. Нахождения суммы элементов в массиве из 10 байт.

- Нахождения количества нечетных чисел в массиве из 8 байт.

- Нахождения суммы отрицательных чисел в массиве из 15 байт.

- Нахождения количества отрицательных чисел в массиве из 20 байт.

- Нахождения суммы четных чисел в массиве из 10 байт.

- Нахождения количества четных чисел в массиве из 15 байт.

- Нахождения суммы нечетных чисел в массиве из 8 байт.

- Нахождения количества нулей в массиве из 16 байт.

- Преобразования массива чисел по следующей формуле: Ci=2Ai+128, i=0..9.

- Преобразования массива чисел по следующей формуле: Ci=2Ai+Bi/2, i=0..15.

- Преобразования массива чисел по следующей формуле: Ci=Ai/4+16, i=0..19.

- Переставляющей элементы массива из 8 байт в обратной последовательности.

14. Нахождения максимального и минимального элементов в массиве из 10 байт и замены их местами.

- Нахождения суммы трех наибольших чисел в массиве из 16 байт.

16. Замены отрицательных чисел в массиве из 16 байт нулями.

17. Замены минимального числа в массиве из 10 байт нулем.

18. Замены четных чисел в массиве из 20 байт нулями.

Приложение Б

(справочное)

Архитектура ЦПУ MSP430

ЦПУ MSP430 имеет следующие особенности:

— RISC-архитектура, поддерживающая 27 команд и 7 режимов адресации;

— ортогональная архитектура — с каждой из команд может использоваться любой режим адресации;

— полная доступность регистров, включая счётчик команд, регистры состояния и указатель стека;

— однотактные регистровые операции;

— большой 16-битный регистровый файл, уменьшающий количество обращений к памяти;

— 16-битная шина адреса, обеспечивающая прямой доступ и ветвление во всём диапазоне адресов;

— 16-битная шина данных, позволяющая напрямую оперировать 2-байтными значениями;

— генератор констант формирует шесть наиболее часто используемых значений, уменьшая размер кода;

— прямой обмен данными между ячейками памяти без промежуточной записи в регистр;

— одно- и двухбайтные адресация и форматы команд.

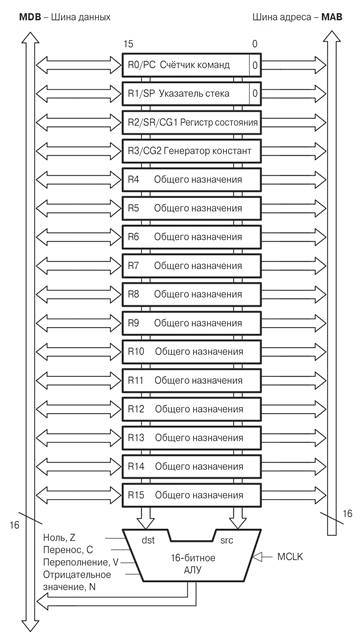

Блок-схема ЦПУ приведена на рисунке Б.1.

Центральный процессор содержит шестнадцать 16-битных регистров. Регистры R0, R1, R2 и R3 имеют специальные функции. Регистры с R4 по R15 являются рабочими регистрами общего назначения.

16-битный счётчик команд (PC/R0) указывает на следующую команду, которая будет выполняться. Указатель стека (SP/R1) используется ЦПУ для сохранения адресов возврата из подпрограмм и прерываний. Указатель стека и счетчик команд могут использоваться со всеми командами и любыми режимами адресации.

Рисунок Б.1 – Блок-схема ЦПУ

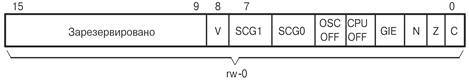

Использовать регистр состояния (SR/R2) в качестве регистра-источника или регистра-приёмника могут только команды, оперирующие двухбайтными значениями и только при использовании режима регистровой адресации. Прочие комбинации режимов адресации используются для поддержки генератора констант. Формат регистра состояния SR приведён на рисунке Б.2.

Рисунок Б.2 – Формат регистра состояния

Назначение битов регистра SR описано в таблице Б.1.

Таблица Б.1 — Биты регистра состояния

| Бит | Описание | ||

| V | Флаг переполнения. Этот бит устанавливается, если результат арифметической операции выходит за границы допустимых значений для знаковых величин | ||

| ADD(.B), ADDC(.B) | Устанавливается, когда:Положительное + Положительное = Отрицательное,Отрицательное + Отрицательное = Положительное,в противном случае сбрасывается | ||

| SUB(.B), SUBC(.B), CMP(.B) | Устанавливается, когда:Положительное – Отрицательное = Отрицательное,Отрицательное – Положительное = Положительное,в противном случае сбрасывается | ||

| SCG1 | Системный тактовый генератор 1. Когда этот бит установлен, сигнал SMCLK отключён | ||

| SCG0 | Системный тактовый генератор 0. Когда этот бит установлен, генератор DCO выключен,если сигнал DCOCLK не используется для формирования сигналов MCLK или SMCLK | ||

| OSCOFF | Выключение генератора. Когда этот бит установлен, кварцевый генератор LFXT1 выключен,если сигнал LFXT1CLK не используется для формирования сигналов MCLK или SMCLK | ||

| CPUOFF | Выключение ЦПУ. Когда этот бит установлен, ЦПУ выключено | ||

| GIE | Общий бит разрешения прерываний. Когда этот бит установлен, маскируемые прерывания разрешены. После сброса все маскируемые прерывания запрещены | ||

| N | Флаг отрицательного результата. Этот бит устанавливается, если результат арифметической операции отрицателен, и сбрасывается, если результат положителен | ||

| Операции со словами | Бит N равен значению 15-го бита результата | ||

| Операции с байтами | Бит N равен значению 7-го бита результата | ||

| Z | Флаг нуля. Этот бит устанавливается, если результат арифметической операции равен нулю, и сбрасывается в противном случае | ||

| C | Флаг переноса. Этот бит устанавливается, если при выполнении арифметической операции возникает перенос, и сбрасывается, если переноса не возникает | ||

Приложение В

(справочное)

Организация памяти микроконтроллеров семейства MSP430

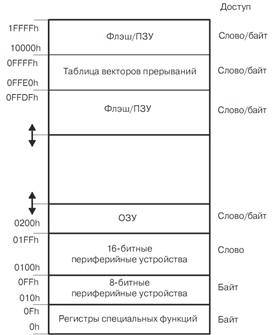

Семейство MSP430 имеет фон-неймановскую архитектуру с единым адресным пространством для регистров специальных функций (SFR), периферии, ОЗУ и Flash-памяти в соответствии с рисунком Б.1. Конкретное распределение памяти можно узнать из справочных данных на интересующее устройство. Доступ к программному коду выполняется всегда по четным адресам. Данные могут быть доступны как байты или как слова. В настоящее время общий объем адресуемой памяти составляет 128 КБ.

Рисунок В.1 – Карта памяти

Флэш/ПЗУ

Начальный адрес области флэш/ПЗУ зависит от объёма этой памяти и отличается для разных устройств. Конечный адрес области флэш/ПЗУ всегда равен 0x1FFFF. Флэш-память может использоваться как для хранения кода, так и для хранения данных. Двухбайтные и однобайтные данные (или таблицы данных) могут располагаться во флэш-памяти и использоваться непосредственно оттуда, без предварительного копирования в ОЗУ.

Таблица векторов прерываний

Таблица векторов прерываний занимает верхние 16 слов нижней области памяти размером 64КБ. При этом вектор прерывания с наивысшим приоритетом располагается в последнем слове области по адресу 0x1FFFF.

ОЗУ

ОЗУ начинается с адреса 0200h. Конечный адрес ОЗУ зависит от объема представленной памяти и различается для каждого конкретного устройства. ОЗУ может использоваться как для программного кода, так и для данных.

Периферийные устройства

Периферийные модули отображены в адресном пространстве. Адреса с 0100h до 01FFh зарезервированы для 16-разрядных периферийных модулей. Они будут доступны с помощью команд-слов. Если используются однобайтные команды, допустимы только четные адреса, при этом старший байт результата всегда будет содержать «0». Адресное пространство с 010h по 0FFh зарезервировано для 8-разрядных периферийных модулей. Эти модули доступны с помощью однобайтных команд. Чтение байтов модулей с помощью команд-слов приведет к появлению в старшем байте непредсказуемого содержимого. Если в байт модуля будут записываться данные в виде слова, то в регистре периферийного модуля сохранится только младший байт этого слова, старший будет проигнорирован.

Регистры специальных функций (SFR)

Некоторые функции периферийных устройств конфигурируются посредством регистров специальных функций. Эти 8-битные регистры располагаются в младших 16 байт адресного пространства. Для обращения к указанным регистрам можно использовать только команды, оперирующие байтами. Назначение отдельных битов регистров специальных функций описано в документации на конкретные модели.

Приложение Г

(справочное)

Статьи к прочтению:

Программирование микроконтроллеров: Урок 2. Организация памяти данных(регистры)

Похожие статьи:

-

Внутренняя организация мп семейства 80х86 в реальном режиме работы

В реальном режиме работы (например, под управлением MSDOS) любой из процессоров семейства 80х86 функционирует просто как 16-разрядный быстрый МП 8086,…

-

Типы памяти микроконтроллеров: память программ, память данных, регистры.

В микроконтроллерах используется три основных вида памяти – это память программ, память данных и регистры. Память программ представляет собой постоянную…